|

||

|

||

| ||

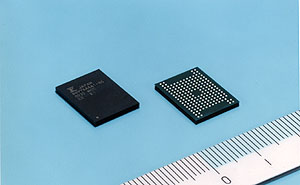

Fujitsu announces new 6-chip PS-MCP flash memories Palm TungstenW: new GSM/GPRS wireless color-display PDA Hitachi announced 17-inch LCD for gamers JEDEX Conference Beijing: DDR-II, Hammer, AMD roadmap specified Fujitsu announces new 6-chip PS-MCP flash memories Fujitsu announced the development of new memory chips, including 6 chips of various purpose, packed into single Package Stacked Multi Chip Package (PS-MCP). MB84VY6A4A1 have 179-pin BGA and are sized similar to the current 4-chip Fujitsu products 15x11x1.4 mm. At that their capacity is 20% higher. A chip includes three 128 Mbit NOR memories with page mode support, two 64 Mbit FCRAM, and one 8 Mbit SRAM. Fujitsu plans to produce new 6-chip products early in November. Theyll be mainly intended for the mobile and PDA markets. MB84VY6A4A1 samples will cost about $65.

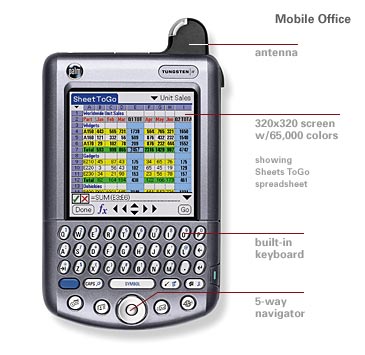

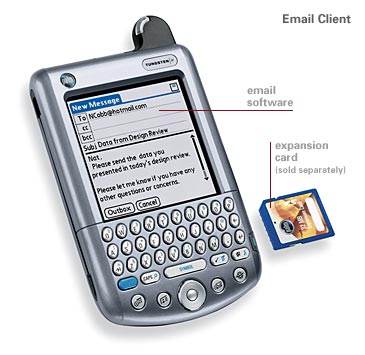

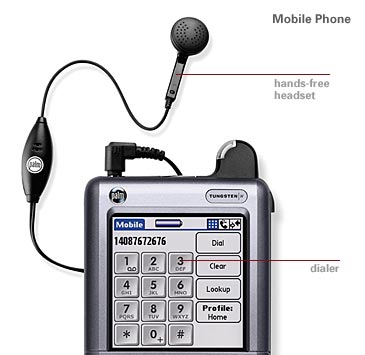

Palm TungstenW: new GSM/GPRS wireless color-display PDA Today Palm announced new Palm Tungsten W PDA, the first Palm´s product with integrated tri-band GSM/GPRS module.   Palm Tungsten W features:

Last week JEDEX brought the first info about draft specs of next-generation DDR-III SDRAM. These very provisional DDR-III SDRAM features include 800 Mbps throughput with consequent increase to 1.5 Gbps. DDR-III power requirements will also be different, making 1.2V or 1.5V (against 1.8V of DDR-II and 2.5V of the current DDR). According to Infineon Technologies, typical capacity of the first DDR-III SDRAM chips will make 4 Gbit. JEDEC will approve final DDR-III specs closer to the end of 2005 along with the first appearance of samples. DDR-III volume production is expected in 2007. DDR-III is expected to feature short-loop through (SLT), the signaling technique, also used in some DDR-II devices to reduce noise at high frequencies. SLT eliminates "stubs" that branch off to carry the signal from the memory bus to each module in the system. The multiple data lines are vulnerable to greater noise at the very high frequencies of new-generation memory chips. SLT connects a series of controller drivers directly with each memory module to reduce noise and signal reflection. The technique is aimed at servers to enable the addition of eight DIMMs per channel, or four times more than with the basic DDR-II configuration. JEDEC sources at the conference said that SLT is similar to the technique used in Rambus Inc.´s RDRAM. They said that SLT is based on designs that go back to 1970 and aren´t included in Rambus´ patents. JEDEC is also drafting an addendum to the DDR-II standard that would cover 2Gbit chips expected in 2005. DDR-II specs also has been amended to double the number of memory banks to eight for 1Gbit and higher-capacity chips. The increased number of banks reduces latency and boosts memory chip efficiency. All DDR-II memory modules will use new BGA packaging because of its smaller form factor. Source: Silicon Strategies

Hitachi announced 17-inch LCD for gamers Hitachi America announced new 17-inch CML174 LCD monitor with claimed twice lower response time than most of current LCDs.CML174 specifications:

JEDEX Conference Beijing: DDR-II, Hammer, AMD roadmap specified JEDEX Conference, finished last week in Peking, brought some details about AMD plans for using DDR-II along with specified processor roadmap.Already in September online press discussed integrated memory controllers of Hammer family that supported only DDR-I. That time we got to know that DDR-II will require a special core version. In his speech Fred Weber, CTO and vice president, officially reported that the first integrated memory controllers of server Opteron Hammers and desktop ClawHammers will support only DDR-I. The next generation of chips will feature DDR-II. Besides, he specified changes in desktop AMD Hammer roadmap, dimly formed at the press conference two weeks ago. Now, according to the roadmap, desktop Hammer systems will appear along with server Opteron in H1 2003. Nevertheless, he also underlined that in the desktop market AMD pin hopes on Barton (Athlon XP with bigger L2 cache). Some more officially confirmed facts: both server, and desktop Hammers will have 1MB L2 cache. Opterons will support up to 8GB single-channel memory or up to 16GB dual-channel. Special version, supporting up to 32GB, will also be released. Theres still no official info about Hammer chips initial clocks, however, Fred Weber, mentioned Opteron 2GHz measurings, saying that SPECint results enable to name it the most powerful server processor. Source: Silicon Strategies

Write a comment below. No registration needed!

|

Platform · Video · Multimedia · Mobile · Other || About us & Privacy policy · Twitter · Facebook Copyright © Byrds Research & Publishing, Ltd., 1997–2011. All rights reserved. |