More details on Intel Madison and Montecito

Intel posted additional details on the development of its 64-bit processor series, including Madison and Montecito, and released a new arbiter bus technology for handling two and more processor cores in a single body.

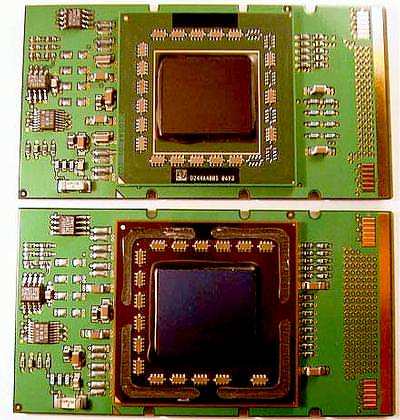

First of all, the company confirmed that new-generation 64-bit Madison will be shipped as scheduled, i.e. in mid-2003. For the first time Intel defined the number of processors in this new line. There will be three Madison variants with different clock rates and cache size. Being made using 0.13-micron process technology, theyll feature 410 million transistors, 3Mb / 4Mb / 6Mb L3 cache size and 1.3V core voltage. The crystal square of a 6Mb L3 cache variant will make about 374mm² (vs. 421mm² of 0.18-micron McKinley with 3Mb L3 cache).

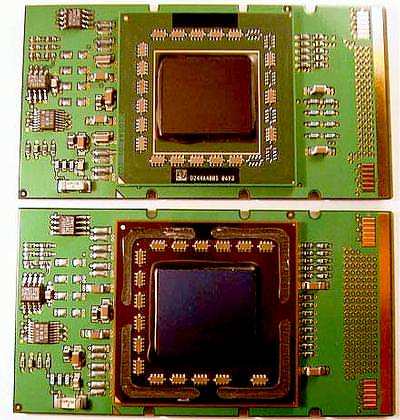

upper one Madison, 6Mb L3 cache, lower McKinley, 3Mb L3 cache

New processors clock speed are supposed to be about 1.5GHz, however this has to be confirmed. Madison chips will consume about 130W of energy, i.e. about the same as the existing McKinleys.

The next generation of Intel´s 64-bit processors expected in 2004 will include chips codenamed Madison 9M and Deerfield. Madison 9M will have 9Mb L3 cache, 1.5GHz+ clock speeds and over 500 million transistors. Deerfield is to be a low-power version of a rackmount Madison variant.

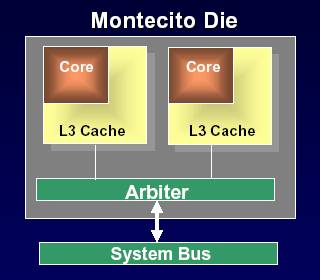

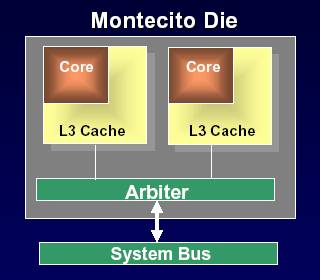

Much more light was shed on dual-core Montecito line, which release date had been moved to 2005 from 2004. Each core is expected to feature own L1, L2, L3 cache (at least 18Mb per body; about 1 billion transistors total).

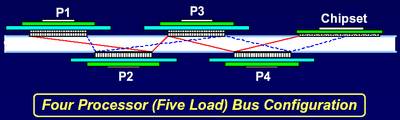

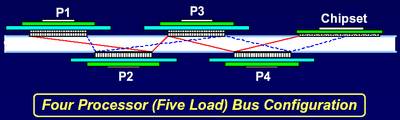

The new arbiter bus technology that to debut here is a kind of a common processor system interface with up to 6.4Gb/s throughput and up to 400 million transactions per second performance. According to the company the bus will enable to double cache size of each processor.

Despite the bus is meant for Montecito dies, Intel doesnt rule out other multicore solutions in the future supporting this technology as well. At the last Microprocessor Forum Intel reported plans for Itanium2 family supposed to feature four cores per body.

Write a comment below. No registration needed!

|

|