The second day is dedicated to server and mobile innovations. During the "Getting IT Right the First Time: Balancing Platform Innovations" presentation Mike Fister, Senior Vice President, General Manager, Enterprise Platforms Group, and Bill Siu, Vice President, General Manager, Desktop Platforms Group, introduced company´s vision of a balanced performance platform on Intel Xeon and Itanium and informed on these platform components roadmap.

This news is dedicated to server innovations.

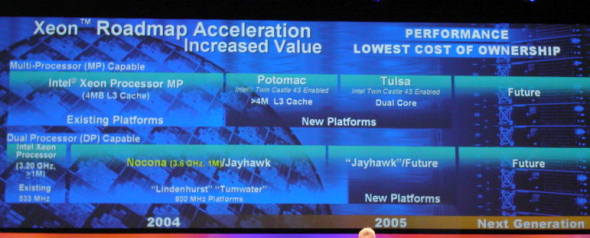

According to information we have, already in this quarter we should expect the new Xeon MP processors on Gallatin core: 3GHz with 4MB L3 cache, 2.7GHz and 2.2GHz with 2MB L3 cache.

Q2 should bring us 2.8GHz to 3.6GHz LGA775 Xeon DP processors on 90nm Nocona core, with 800MHz FSB support, 1MB L2 cache, SSE3 instruction set, Clackamas/IA32E, and Demand Based Switching (DBS) power management technology. At the same time the company is to present E7515 chipset codenamed Tumwater.

Already in Q2 2004 Intel is to introduce 2.8GHz+ low-voltage Nocona solutions. And closer to the year-end the Xeon MP family is to be extended with about 4GHz Potomac core and TwinCastle chipset. By that time we should expect 4GHz LGA775 Xeon DP chips on Jayhawk core coupled with Lindenhurst chipset.

Both Jayhawk and Potomac will be made using 90nm process. Featuring 2MB L2 cache, they will support 800MHz FSB, TNI (Tejas New Instructions), and Clackamas/IA32E.