| « | » |

Enhanced SpeedStep technology

And now let's proceed to the "dessert", the hit of new Intel Xeon processors with Nocona core – Enhanced SpeedStep technology for servers (code name – DBS, Demand-Based Switching), which was demonstrated so well on Intel Developer Forum 2004 Russia.

Enhanced SpeedStep initially appeared in Pentium M processors as a replacement of Intel SpeedStep (used in mobile processors Pentium III and Pentium 4) for more effective power consumption management. This is done by changing dynamically P-state transitions, each P-state is set by a combination of FID and VID values). The improved nature of SpeedStep consists in the centralized control mechanism (its integration into CPU core) and the program interface (in the form of model-specific registers). Enhanced SpeedStep is indicated by the corresponding CPUID flag. Processor MSR is used to control this technology (IA32_MISC_ENABLE, MSR_PERF_STATUS and MSR_PERF_CTL).

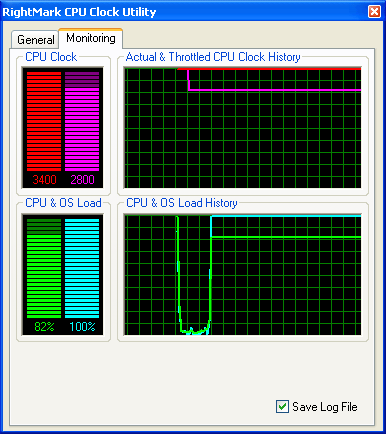

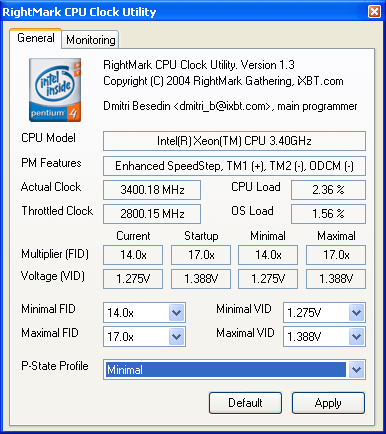

On the quality level (that is from the point of view of a description), Enhanced SpeedStep in Xeon processors for servers looks the same, while its implementation may be significantly different. Well, why not examine the behaviour of this new technology? We restore the standard CPU mode (TM1 should be enabled just for the record), run RMClock, set the CPU performance/power consumption level to minimum (P-state profile: Minimal). To be more illustrative, let's apply 100% load to the processor. Here are the results...

|

|

Did you expect anything different? We didn't. No need in commenting, but we'll do it anyway: the actual CPU clock remains unchanged, CPU load and throttled CPU clock go down to 82% and 2800 MHz correspondingly. It means that Enhanced SpeedStep for servers (in our opinion) is just another modification of the CPU clock modulation mechanism. But in this case it's much closer to TM2 in its implementation, because it can also modify CPU voltage. The difference is that it snaps into action "on demand" instead of being triggered by overheating.  |

|

|

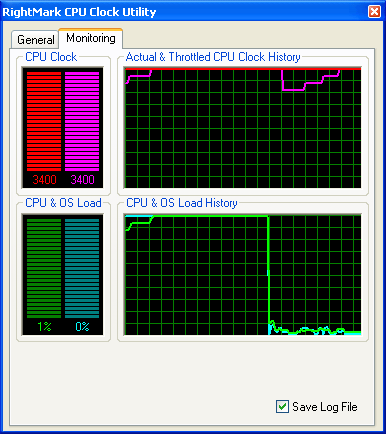

For conscience sake, we tried to set other CPU "multiplier" values – steadily increasing it from 14x to the nominal 17x. The result is quite obvious, throttled CPU clock changes at full CPU load as well as in the idle mode. Let's dwell on changing CPU voltage as a more important component of Enhanced SpeedStep (as well as TM2). It's not so easy to enable – if BIOS does not properly initialize a processor (the way it's recommended by the manufacturer), you will have to sweat it out. Let's use CPUMSR again. So, first of all, enable TM2 instead of TM1. Then, change FID/VID values for TM2 target. Minimum voltage has to be set "blindly" (as we have already said, the table of VID values in CPUMSR is wrong).  |

|

|

You can see the result – we have turned the trick. On the second screenshot you can see that we can swap TM2 back with TM1 – processor still acts correctly. In conclusion it should be noted that we had no opportunity to rate the real changes in CPU voltage (because we had no system monitoring software for this chipset/motherboard). That's why we made use of a rude method – we set the minimum voltage to 1.000 V. The system instantly rebooted – it means the core voltage had really changed (to an inadmissibly low level).

[an error occurred while processing this directive] |