| « | » |

Automatic thermal monitoring mechanism #2

Thermal Monitor 2 (TM2) is an advanced mechanism of CPU overheating protection, implemented in Pentium M processors and, according to Intel, in new Pentium 4 models (nevertheless, you can currently see it only in the server modification – Xeon Nocona). A considerable difference of the new mechanism is that TM2 (as the manufacturer claims) can control the frequency (to be more exact, FID – FSB frequency multiplier) and CPU voltage (VID), while TM1 modulates CPU clock. Due to reduced voltage, TM2 allows to retain better processor performance in case of overheating at the same reduction of power consumption level. TM2 can be detected using the CPUID instruction, and it can be controlled by MSR (IA32_MISC_ENABLE and MSR_THERM2_CTL). Note that TM2 is implemented in Pentium M and Pentium 4 (Xeon) processors differently. Target FID and VID values are important TM2 parameters and a processor should switch to them in case of overheating (the latter is indicated by the same sensor as used in TM1).

Responsibility for TM2 usage is laid on BIOS. TM2 is recommended for 2.8 GHz processors and higher (166 MHz bus) and 3.6 GHz and higher (200 MHz bus), while TM1 is recommended for junior models. It's a non-standard CPU mode to enable or disable both TM1 and TM2 at the same time, thus it's not recommended by the manufacturer. Target FID and VID values should be set by BIOS at the CPU initialization process. A typical target FID is minimum possible (14x) and the recommended VID is 1.275 V.

It's high time to test TM2 on a Xeon Nocona processor (no other options available so far). As BIOS does not allow to choose thermal monitoring modes at will, we'll start CPUMSR (later on we shall add specific CPU settings into RMClock), disable TM1 and enable TM2. We don't change the target FID and VID settings (considering that the table of VID values in CPUMSR is just wrong). After that we run RMClock.

|

|

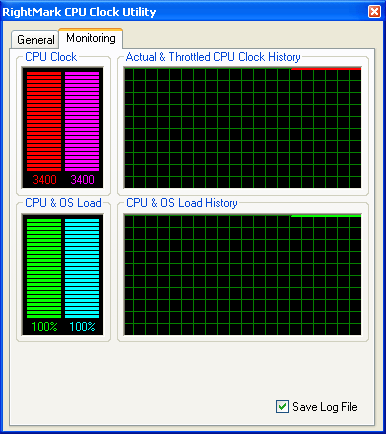

The changes are applied – the processor uses TM2 instead of TM1. What concerns target frequency and voltage settings, you can easily see (Minimal FID/VID indicators) that BIOS set them to 14x and 1.388V (standard CPU voltage), which means that the processor will not change its voltage when switched to TM2 mode. This is irrelevant for our purposes – we cannot estimate the actual power consumption of a processor anyway. So, 100% load is already applied to the processor, we only have to... stop the cooler fan.

And what do we see? Actual CPU clock (TSC clock frequency) remains... unchanged! But the drop of CPU load and throttled CPU clock is obvious – with the same typical surges on the curve. Throttling starts in 1 minute 30 seconds and ends at the second minute with the 82% load and the throttled CPU clock of 2800 MHz sharp. That is the final state, marked by the 14x "multiplier" (so to speak), can be considered reached. But there is one important reservation: it was not the actual CPU clock that was reduced, but only an effective clock, which we call the "throttled CPU clock". What does it mean? Perhaps, the processor is really capable of reducing its clock frequency (according to Intel's documentation), but it does it so intricately that we just cannot see it. Or maybe it cannot do that – God knows, we don't :). As the CPU manufacturer does not provide a "valid" official method to measure CPU clocks in Pentium 4 / Xeon processors, which would take into account their performance and power consumption management technologies, we have nothing to do but to assume that TM2 is the very same... CPU clock modulation. But for one vital difference (from TM1): in TM2 mode a processor can reduce its clock modulation together with voltage.

Power on the cooler. The picture is evident and requires no explanations.

[an error occurred while processing this directive] |