| « | » |

New revision of Nocona core in Intel Xeon processors

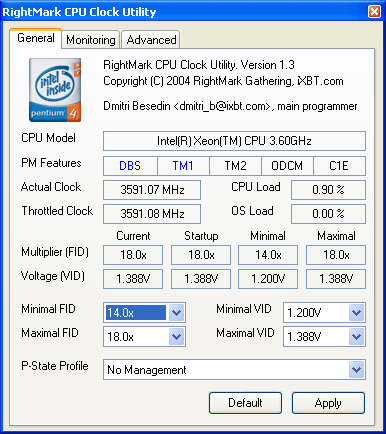

And finally, let's review a similar E0 revision (CPUID = 0F41h) of Nocona core in Intel Xeon 3.6 GHz processors. At first we'll study which of the reviewed power management technologies are available and enabled by default in this group of processors.

|

|

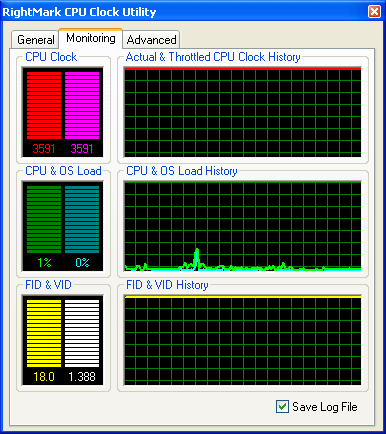

So, the new revision of Nocona core supports all five "thermal" technologies – from "ancient" ODCM and TM1 to the new TM2, DBS, and C1E. The following technologies are enabled at startup – DBS (by the way, you can enable/disable the Enhanced SpeedStep for servers in BIOS settings; besides, it's automatically enabled by RMClock at startup) and, strange as it may seem, the old modification of thermal throttling – automatic thermal monitoring mechanism #1 (TM1), unlike the 3.6 GHz Pentium 4. Interestingly, BIOS sets target FID/VID for TM2 correctly (you can see that by Minimal FID/VID), but for some reason this technology is not enabled by default. And finally, C1E is also disabled by default (it can be enabled/disabled in BIOS), which is clearly demonstrated on the right screenshot: FID/VID values do not change in time. One can assume that disabled C1E on a server platform is dictated by maximum performance issues (minimum server response time to requests): both entering C1E and leaving it are accompanied with larger delays compared to entering/leaving the regular C1 (HALT) state, due to necessary switching between CPU operating modes (FID/VID) to lesser power consumption and back. No matter what manufacturers of processors, chipsets, and motherboards do with their products, we can always enable necessary options manually, using the Advanced tabbed page in RMClock. Let's enable TM2 (actually we could have left it disabled), C1E, and see the results.  |

|

|

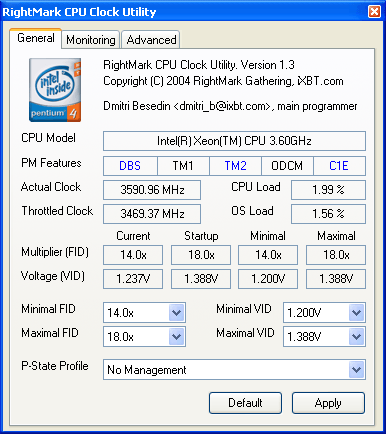

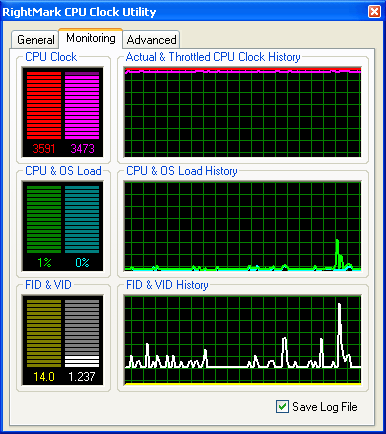

C1E in action. CPU multiplier dropped to the minimum 14x (that is according to our working hypothesis, the CPU clock was modulated with 77.7% duty cycle), the core voltage started to "jump" between minimum and maximum, being mostly at 1.237V. The effective CPU clock went down, its minimum level being at about 3470 MHz. So, C1E in Xeon (Nocona) processors works correctly.

And now let's see how the two latest functions of controlling CPU operating modes (Enhanced SpeedStep (DBS) for servers and Enhanced Halt State (C1E)) work together. These days such a situation can be demonstrated only by the latest Intel Xeon processors. Let's set the minimum FID/VID to 14x and 1.2V correspondingly and then use RMClock to set P-State Profile to Minimal.

Here are the results: the effective clock is reduced to ~2.8 GHz, FID/VID – to the requested 14x and 1.2V. C1E technology is sort of disabled – effective CPU clock as well as its voltage cannot be any lower. Let's proceed: set the P-State Profile of the processor to Maximal (FID = 18x, VID = 1.388V).

The processor demonstrates curious behaviour in this mode: C1E obviously "prevails" over Enhanced SpeedStep despite the forced maximal FID/VID – the effective CPU clock goes down, FID and VID oscillate between the minimal and maximal levels. That is now DBS is "sort of disabled", not C1E. Another experiment: we'll retain the Maximal P-State Profile, but... the voltage will be reduced to minimum (this is quite possible, when a CPU is not loaded), that is FID/VID will be set to 18x and 1.2V.

Now C1E is really disabled, complete control is passed to DBS. So we can draw an interesting conclusion: to make the C1E technology possible, CPU voltage (VID) must differ from the minimum possible voltage (set in TM2 Target VID) at least by 0.0125V. In other words, first of all various CPU performance/power consumption states mean VID values for C1E, while FID values are secondary.

[an error occurred while processing this directive] |