| « |

Summing it all up

Our previous article started and the present one finished the review of modern performance and power management technologies in Intel Pentium 4 (Prescott) and Intel Xeon (Nocona). The main conclusion has been already made – all the technologies reviewed, from the first ODCM to the latest Enhanced SpeedStep (DBS) and Enhanced Halt State (C1E) seem to be based on a common idea – CPU clock modulation (duty cycle). It may seem "unfair", cheating consumers. That's not the case, of course. We have never said that. In fact, it's just one of possible (and the simplest) ways to implement these technologies, but it's no less effective than "more honest" ways. Besides, don't forget that it's one of possible opinions (of the author), with which you may just as well disagree. You can think of an alternative opinion, much more "correct" according to the official Intel's documentation.

But what is a possible alternative? Considering that some processor units (e.g. bus arbiters, asynchronous prefetchers, etc) most likely cannot easily switch between various performance modes, one can assume that Intel engineers most likely "divided" the processor core into several individually clocked components (due to several PLL, or due to prescalers transforming the reference clock). Some of these components always operate at full clock (including Time Stamp Counter, its readings are used in the conventional method for measuring CPU clock), while the other components (executive modules) can operate at lower clocks. It's not quite clear though why Intel engineers decided that TSC should operate at full clock, while Performance Monitoring Counters (PMC) operate at "reduced" clock?

Possible explanations of this fact as well as the choice between the above mentioned opinions are up to our readers. What concerns us, we didn't find any experimental evidence of the second, more "official" hypothesis in the course of our research. Of course, we have no obvious evidence of our point of view, except for the fact that it does not contradict the experimental facts. So let's apply the rule of contraries. The main contradictions to our opinion are (1) the incorrect CPU clock measuring technique and (2) our announcement that Pentium 4 and Xeon processors can operate at full clock at reduced voltage (in TM2, DBS and C1E modes).

Let's start with the first contradiction. There is no doubt that the actual CPU clock is measured correctly – this method is used by all system utilities (CPU-Z, WCPUID) without exception, the operating system itself, as well as... by Intel Processor Identification Utility! The screenshot below is taken on an Intel Xeon 3.6 GHz processor with enabled Enhanced SpeedStep.

In our opinion, no comments are necessary: CPU clock is measured by TSC (3.6 GHz), and the FSB clock is measured by dividing it by the current 14x multiplier, which results in the wrong value of 1028 MHz and an illustrative label "Overclocked!". So, if the "wrong" method is used by Intel's utilities as well, what is a "correct" method then? Such formulas as

FSB_freq = TSC_freq / Startup_FID

CPU_freq = FSB_freq * Current_FID,

i.e. multiplying the FSB clock by the current multiplier? (to all appearances this method was used to demonstrate DBS at IDF 2004 Russia) Sorry, this is not measuring but mere adjusting, wishful thinking. Besides, it obviously cannot be an all-purpose method, that is it will not be good for any x86-compatible processor.

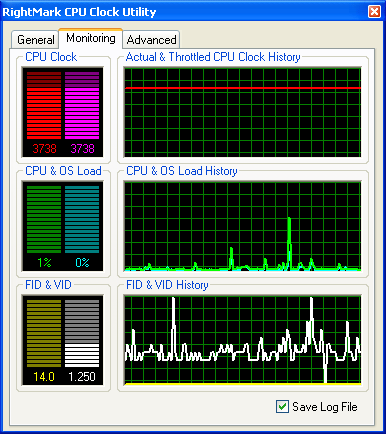

Now what concerns the second statement. At first sight it looks evident: reduced CPU voltage (when TM2 snaps into action with enabled Enhanced SpeedStep and Enhanced Halt State) must result in the reduced actual CPU clock. But that's only the first impression – the facts speak of the contrary. First of all, have a look at the last screenshot in the previous chapter – you will clearly see that the Intel Xeon 3.6 GHz processor can operate at full clock (FID = 18x) at quite a low voltage – 1.2V (0.1875V lower than nominal!). And secondly, let's carry out another interesting experiment – take an unlocked Intel Pentium 4 560J (Prescott) 3.6 GHz processor and make it think that it operates at the minimal clock (FID = 14x), but... raise the FSB clock to 266 MHz (we described this procedure in detail in the article "Unveiling DDR2-533 Potential. Part 2: 266 MHz FSB, Intel Pentium 4 Prescott processor").

|

|

Look what happens: the processor is sure that it still operates in standard mode; so it controls its voltage dynamically in the halt state using the C1E technology. But its real clock (both actual and effective) is equal to 3.74 GHz. So, Pentium 4 and Xeon processors can actually operate at full clock at reduced voltage, if they are in the halt state (C1/C1E). Thus, the facts mentioned above don't corroborate, but just support our conclusion that the performance and power management functions in Intel Pentium 4 and Xeon processors have the same basis.

[an error occurred while processing this directive] |