VIA Technologies is one of the leaders in making chipsets and processors;

the Taiwanese giant is attacking more aggressively these days, and Intel

has to do its best to maintain its position not to mention development

of new markets.

VIA's press conference held in Hannover at CeBIT 2003 gathered the largest

audience, except ATI (the hall provided couldn't house all listeners).

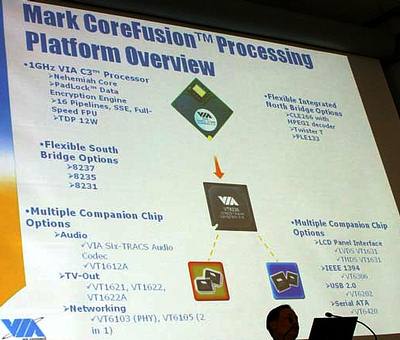

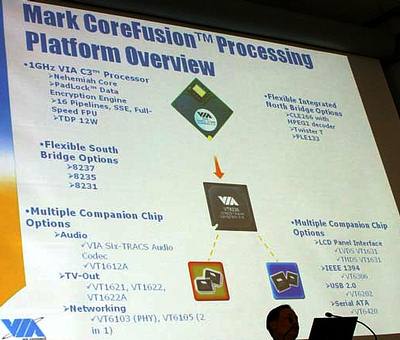

In the news we mentioned that VIA started a new processor project named

Mark CoreFusion. At CeBIT VIA disclosed more information.

The main idea of Mark CoreFusion is integration of the north bridge into

VIA C3 processor. It must be something average of C3 (namely, Nehemiah)

and CLE266 in one package. The next step is integration of a south bridge,

like VT8235, into the hybrid processor. Some time ago the company had a

similar project named Matthew chip which was presented yet at CeBIT 2000.

But a bit later the project was frozen. Well, at that time they would hardly

get a more or less efficient solution. By the way, Intel had a similar

project named Timna which was called off as well.

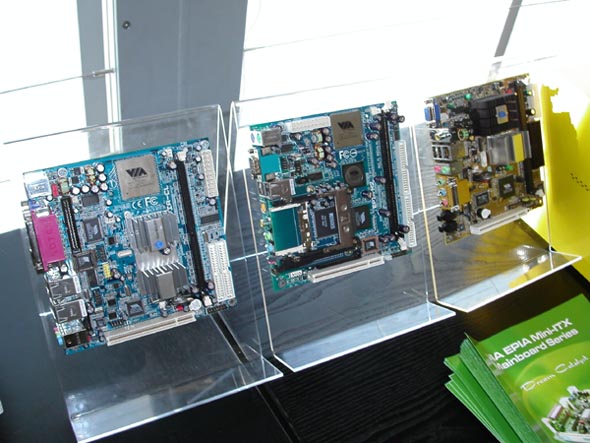

Why is Matthew reanimated? It's simple: the current mini platform EPIA

is quite successful. The companies demonstrated working systems and platforms

at the conference.

Why not to strengthen the success? The Mark chip will actually be a hybrid

chip, which is called MCM (Multi Chip on Module) today. The processor core

and chipset will be produced separately, and they will be integrated on

a single plate according to the market demand for models with a certain

clock speed or customer's wants. As a result, the first-generation Mark

CoreFusion chip will be a hybrid of 1GHz C3 CPU with 1.25V on the core

and power consumption of 12 W, CLE266 north bridge with S3 CastleRock graphics

and MPEG-2 hardware decoding, analog and DVI outputs, SDRAM and DDR SDRAM

interfaces (DDR266). The variations with PM133/266 north bridges (Savage4

graphics) or PLE133 (Trident graphics) are also possible. VT8235 and VT8237

can be used as integrated version of south bridges.

The current sandwich has the total power consumption which couldn't

do without active cooling. The company's aim is to bring Mark CoreFusion

to passive cooling. They stressed on the fact they they didn't target to

reach speed summits with Mark chip.

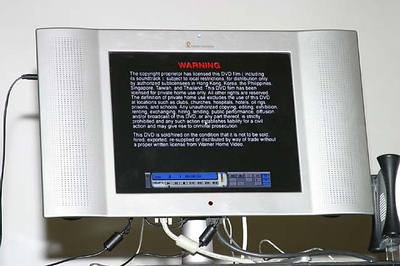

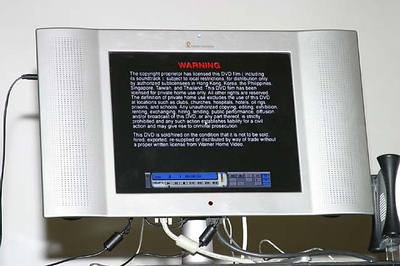

Another important event was announcement of a new miniature Nano ITX

platform meant for Mark CoreFusion series. There are no any details except

the fact that such boards will be smaller than mini ITX form-factor by

15%. With time such platforms might be integrated into LCD monitors. Like

in this prototype:

The company also demonstrated a prototype of Mobile C3 processor named

Antaur.

Mobile C3 Antaur will be built on Nehemiah core and utilize 0.13 micron

technology. It will be packed into 386-pin EBGA (Enhanced Ball Grid Array)

of 35 x 35 mm.

The current prototype is clocked at 1.0 GHz, FSB 133 MHz, 1.25 V on

the core in the full-scale mode. VIA PowerSaver 2.0 supported adjusts core

clock speed and voltage depending on the mode of operation.

It's obvious that VIA Antaur mobile processor and VIA Mark ColdFusion

integrated chip where C3 core is combined with the south and north bridges

are different facets of the same project. Moreover, PowerSaver2.0 technology

is also an integrated part of Mark CoreFusion project.

I hope VIA will soon lift the veil of mystery from this project. Anyway,

it's clear now how they are going to raise its sales volumes up to 6 million

of processors in 2003...

At the conference they also showed notebooks based on C3 processors

and S3 graphics.

Write a comment below. No registration needed!