Renesas Develops Massively Parallel Processor Based On Matrix Architecture

Renesas Technology announced the development of a massively parallel processor based on a matrix architecture suitable for image and audio multimedia data processing.

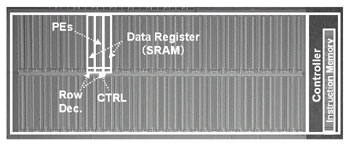

This processor is a massively parallel programmable device implemented in 90-nm CMOS with a core area of 3.1mm² featuring tight coupling of 2,048 processing elements and 1Mbit SRAM, and has been confirmed to achieve 40 GOPS (giga operations per second) performance at a 200 MHz clock frequency 250 mW power dissipation.

The novelty is a fine-grained SIMD (single instruction multiple data) type massively parallel programmable device, featuring the following structural characteristics:

- Basic configuration: 2-bit processing elements (PE) and 512-bit SRAM assigned as data registers.

- 2,048 PEs and a total of 1 Mbit SRAM, together with tight coupling between PEs.

Source: Renesas Technology

Write a comment below. No registration needed!

|

|