IBM officially announces Power5 processor

These days IBM officially announced its Power5 processors alongside two servers on it. This 64-bit novelty is to compete with 64-bit products from AMD, Intel and Sun.

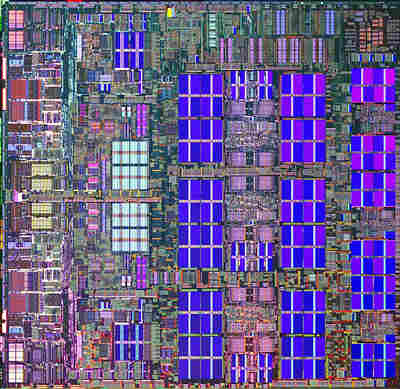

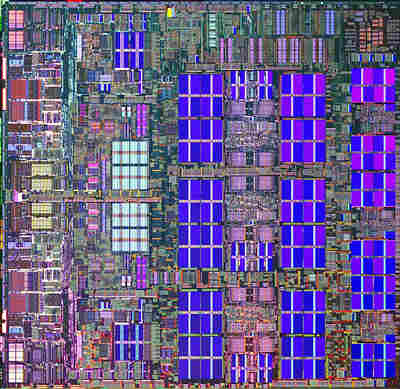

Power5 is made using 130nm silicon-on-insulator (SOI) process with copper interconnects at 300mm fab in East Fishkill. The chip has 389mm² square size and contains 276 million transistors (vs. 174 million transistors of Power4.) The processor features 2,313 signal I/O and 3,057 power I/O units. I guess the latter are used for dissipated heat optimization purposes.

Power5 supports simultaneous multi-threading (SMT) technology that enables simultaneous operation of two Power5 cores.

The first IBM server on Power5 is eServer i5 based on dual chip module (DCM) with Power5 core and L3 cache. In the future the company plans to use quad-processor multi-chip modules (MCM; on the photo,) so Power5-based will contain up to 64 processor cores.

As for eServer i5, it supports up to 40 dynamic software sections, up to 10 hardware-software sections with SMT task time-division, up to 2 hardware sections. The first eServer i5 model (i570) supports up to 32 processor cores.

Write a comment below. No registration needed!

|

|